# Freescale Semiconductor Technical Data

Document Number: MPC8360EEC

Rev. 2, 12/2007

# MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications

This document provides an overview of the MPC8360E/58E PowerQUICC<sup>TM</sup> II Pro processor revision 2.x TBGA features, including a block diagram showing the major functional components. This device is a cost-effective, highly integrated communications processor that addresses the needs of the networking, wireless infrastructure and telecommunications markets. Target applications include next generation DSLAMs, network interface cards for 3G basestations (Node Bs), routers, media gateways and high end IADs. The device extends current PowerQUICC II Pro offerings, adding higher CPU performance, additional functionality, faster interfaces and robust interworking between protocols while addressing the requirements related to time-to-market, price, power, and package size. This device can be used for the control plane along with data plane functionality.

For functional characteristics of the processor, refer to the MPC8360E Integrated Communications Processor Family Reference Manual, Rev. 2.

To locate any published errata or updates for this document, contact your Freescale sales office.

### Contents

| 1.  | Overview                                           |

|-----|----------------------------------------------------|

| 2.  | Electrical Characteristics 8                       |

| 3.  | Power Characteristics                              |

| 4.  | Clock Input Timing                                 |

| 5.  | RESET Initialization                               |

| 6.  | DDR and DDR2 SDRAM                                 |

| 7.  | DUART 26                                           |

| 8.  | UCC Ethernet Controller: Three-Speed Ethernet, MII |

|     | Management                                         |

| 9.  | Local Bus                                          |

| 10. | JTAG 47                                            |

| 11. | $I^2C$                                             |

| 12. | PCI                                                |

| 13. | Timers                                             |

| 14. | GPIO 56                                            |

| 15. | IPIC                                               |

| 16. | SPI                                                |

| 17. | TDM/SI                                             |

| 18. | UTOPIA/POS                                         |

| 19. | HDLC, BISYNC, Transparent, and Synchronous         |

|     | UART                                               |

| 20. | USB 67                                             |

| 21. | Package and Pin Listings 68                        |

| 22. | Clocking                                           |

| 23. | Thermal                                            |

| 24. | System Design Information                          |

| 25. | Document Revision History                          |

| 26. | Ordering Information                               |

# 1 Overview

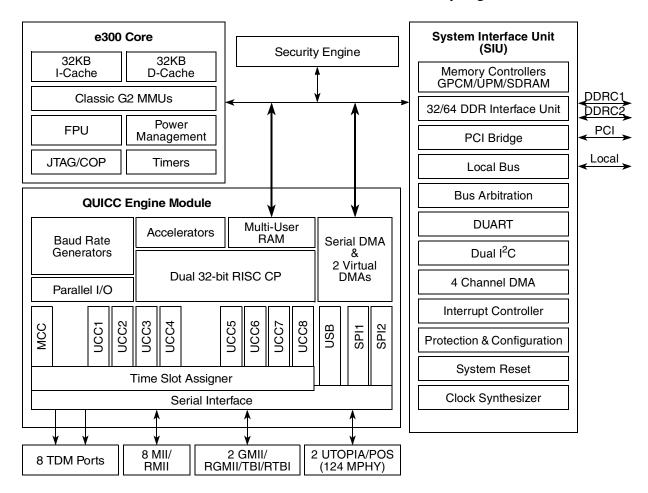

This section describes a high-level overview including features and general operation of the MPC8360E/58E PowerQUICC<sup>TM</sup> II Pro processor. A major component of this device is the e300 core which includes 32 Kbytes of instruction and data cache and is fully compatible with the PowerPC<sup>TM</sup> 603e instruction set. The new QUICC Engine module provides termination, interworking, and switching between a wide range of protocols including ATM, Ethernet, HDLC, and POS. The QUICC Engine module's enhanced interworking eases the transition and reduces investment costs from ATM to IP based systems. The other major features include a dual DDR SDRAM memory controller for the MPC8360E, which allows equipment providers to partition system parameters and data in an extremely efficient way, such as using one 32-bit DDR memory controller for control plane processing and the other for data plane processing. The MPC8358E has a single DDR SDRAM memory controller. The MPC8360E/58E also offers a 32-bit PCI controller, a flexible local bus, and a dedicated security engine.

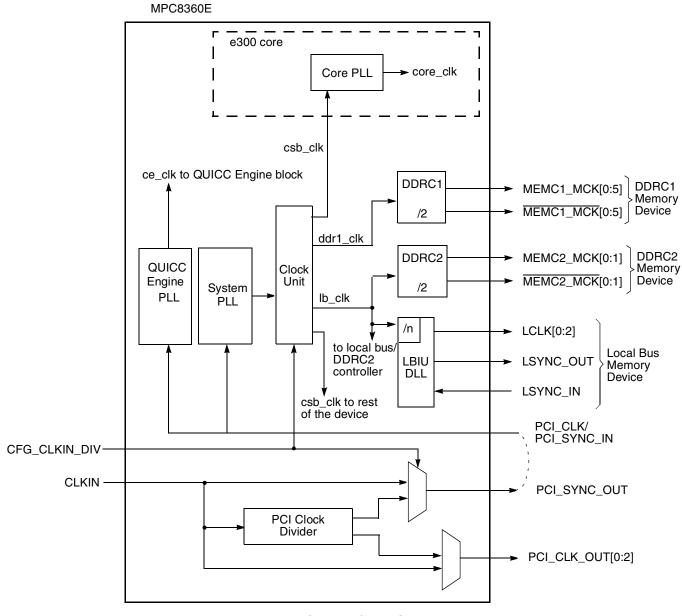

Figure 1. MPC8360E Block Diagram

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

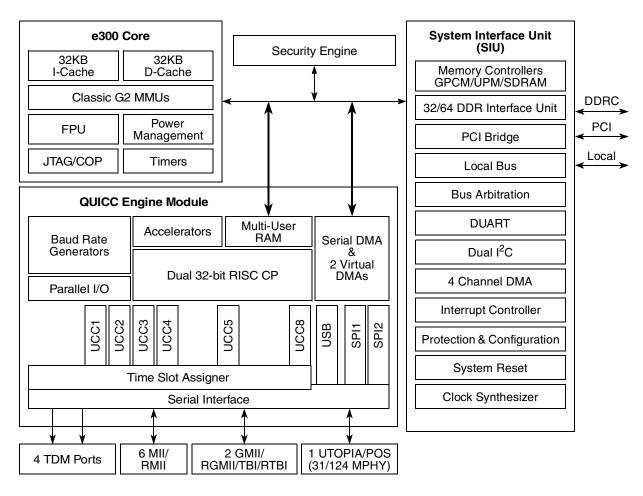

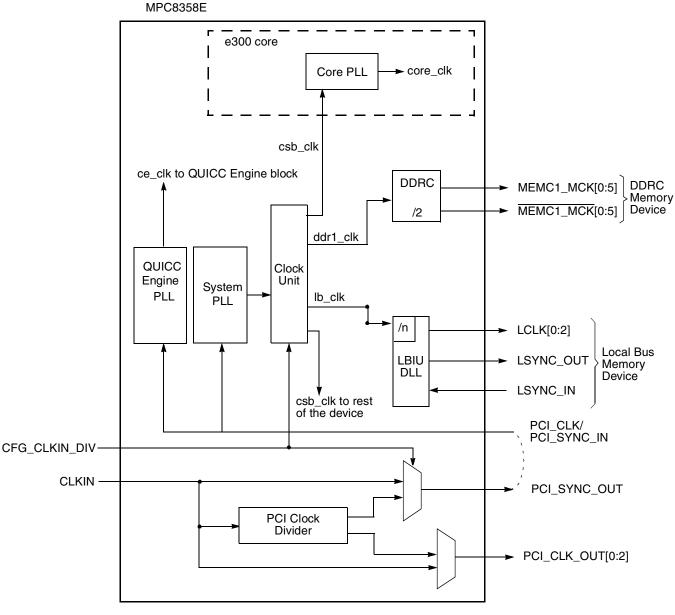

Figure 2. MPC8358E Block Diagram

Major features of the MPC8360E/58E are as follows:

- e300 PowerPC processor core (enhanced version of the MPC603e core)

- Operates at up to 667 MHz (for the MPC8360E) and 400 MHz (for the MPC8358E)

- High-performance, superscalar processor core

- Floating-point, integer, load/store, system register, and branch processing units

- 32-Kbyte instruction cache, 32-Kbyte data cache

- Lockable portion of L1 cache

- Dynamic power management

- Software-compatible with the Freescale processor families implementing the Power Architecture<sup>TM</sup> technology

- QUICC Engine unit

- Two 32-bit RISC controllers for flexible support of the communications peripherals, each operating up to 500 MHz (for the MPC8360E) and 400 MHz (for the MPC8358E)

- Serial DMA channel for receive and transmit on all serial channels

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

### Overview

- QE peripheral request interface (for SEC, PCI, IEEE® Std 1588<sup>TM</sup>)

- Eight universal communication controllers (UCCs) on the MPC8360E and six UCCs on the MPC8358E supporting the following protocols and interfaces (not all of them simultaneously):

- IEEE Std. 1588 protocol supported

- 10/100 Mbps Ethernet/IEEE Std. 802.3® CDMA/CS interface through a media-independent interface (MII, RMII, RGMII)<sup>1</sup>

- 1000 Mbps Ethernet/IEEE Std. 802.3 CDMA/CS interface through a media-independent interface (GMII, RGMII, TBI, RTBI) on UCC1 and UCC2

- 9.6K jumbo frames

- ATM full-duplex SAR, up to 622 Mbps (OC-12/STM-4), AAL0, AAL1 and AAL5 in accordance ITU-T I.363.5

- ATM AAL2 CPS, SSSAR, and SSTED up to 155 Mbps (OC-3/STM-1) Mbps full duplex (with 4 CPS packets per cell) in accordance ITU-T I.366.1 and I.363.2

- ATM traffic shaping for CBR, VBR, UBR, and GFR traffic types compatible with ATM forum TM4.1 for up to 64K simultaneous ATM channels

- ATM AAL1 structured and unstructured circuit emulation service (CES 2.0) in accordance with ITU-T I.163.1 and ATM Forum af-vtoa-00-0078.000

- IMA (Inverse Multiplexing over ATM) for up to 31 IMA links over 8 IMA groups in accordance with the ATM forum AF-PHY-0086.000 (Version 1.0) and AF-PHY-0086.001 (Version 1.1)

- ATM Transmission Convergence layer support in accordance with ITU-T I.432

- ATM OAM handling features compatible with ITU-T I.610

- PPP, Multi-Link (ML-PPP), Multi-Class (MC-PPP) and PPP mux in accordance with the following RFCs: 1661, 1662, 1990, 2686 and 3153

- IP support for IPv4 packets including TOS, TTL and header checksum processing

- Ethernet over first mile IEEE Std. 802.3ah®

- Shim header

- Ethernet-to-Ethernet/AAL5/AAL2 inter-working

- L2 Ethernet switching using MAC address or IEEE Std. 802.1P/Q® VLAN tags

- ATM (AAL2/AAL5) to Ethernet (IP) interworking in accordance with RFC2684 including bridging of ATM ports to Ethernet ports

- Extensive support for ATM statistics and Ethernet RMON/MIB statistics

- AAL2 protocol rate up to 4 CPS at OC-3/STM-1 rate

- Packet over Sonet (POS) up to 622-Mbps full-duplex 124 MultiPHY

- POS hardware; microcode must be loaded as an IRAM package

- Transparent up to 70-Mbps full-duplex

- HDLC up to 70-Mbps full-duplex

- HDLC BUS up to 10 Mbps

- 1. SMII or SGMII media-independent interface is not currently supported

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

5

- Asynchronous HDLC

- UART

- BISYNC up to 2 Mbps

- User-programmable Virtual FIFO size

- QUICC Multichannel Controller (QMC) for 64 TDM channels

- One multichannel communication controller (MCC) only on the MPC8360E supporting the following:

- 256 HDLC or transparent channels

- 128 SS7 channels

- Almost any combination of subgroups can be multiplexed to single or multiple TDM interfaces

- Two UTOPIA/POS interfaces on the MPC8360E supporting 124 MultiPHY each (optional 2\*128 MultiPHY with extended address) and one UTOPIA/POS interface on the MPC8358E supporting 31/124 MultiPHY

- Two serial peripheral interfaces (SPI); SPI2 is dedicated to Ethernet PHY management

- Eight TDM interfaces on the MPC8360E and four TDM interfaces on the MPC8358E with 1-bit mode for E3/T3 rates in clear channel

- Sixteen independent baud rate generators and 30 input clock pins for supplying clocks to UCC and MCC serial channels (MCC is only available on the MPC8360E)

- Four independent 16-bit timers that can be interconnected as four 32-bit timers

- Interworking functionality:

- Layer 2 10/100-Base T Ethernet switch

- ATM-to-ATM switching (AAL0, 2, 5)

- Ethernet-to-ATM switching with L3/L4 support

- PPP interworking

- Security engine is optimized to handle all the algorithms associated with IPSec, SSL/TLS, SRTP, 802.11i, iSCSI, and IKE processing. The security engine contains four crypto-channels, a controller, and a set of crypto execution units (EUs).

- Public key execution unit (PKEU) supporting the following:

- RSA and Diffie-Hellman

- Programmable field size up to 2048 bits

- Elliptic curve cryptography

- F2m and F(p) modes

- Programmable field size up to 511 bits

- Data encryption standard execution unit (DEU)

- DES, 3DES

- Two key (K1, K2) or three key (K1, K2, K3)

- ECB and CBC modes for both DES and 3DES

- Advanced encryption standard unit (AESU)

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

### Overview

- Implements the Rinjdael symmetric key cipher

- Key lengths of 128, 192, and 256 bits, two key

- ECB, CBC, CCM, and counter modes

- ARC four execution unit (AFEU)

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- Message digest execution unit (MDEU)

- SHA with 160-, 224-, or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either SHA or MD5 algorithm

- Random number generator (RNG)

- Four crypto-channels, each supporting multi-command descriptor chains

- Static and/or dynamic assignment of crypto-execution units via an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- Storage/NAS XOR parity generation accelerator for RAID applications

- Dual DDR SDRAM memory controllers on the MPC8360E and a single DDR SDRAM memory controller on the MPC8358E

- Programmable timing supporting both DDR1 and DDR2 SDRAM

- On the MPC8360E, the DDR buses can be configured as two 32-bit buses or one 64-bit bus; on the MPC8358E, the DDR bus can be configured as a 32-bit or a 64-bit bus

- 32- or 64-bit data interface, up to 333 MHz (for the MPC8360E) and 266 MHz (for the MPC8358E) data rate

- Four banks of memory, each up to 1 Gbyte

- DRAM chip configurations from 64 Mbits to 1 Gigabit with x8/x16 data ports

- Full ECC support (when the MPC8360E is configured as 2x32 bit DDR memory controllers, both support ECC)

- Page mode support (up to 16 simultaneous open pages for DDR1, up to 32 simultaneous open pages for DDR2)

- Contiguous or discontiguous memory mapping

- Read-modify-write support

- Sleep mode support for self refresh SDRAM

- Supports auto refreshing

- Supports source clock mode

- On-the-fly power management using CKE

- Registered DIMM support

- 2.5-V SSTL2 compatible I/O for DDR1, 1.8-V SSTL2 compatible I/O for DDR2

- External driver impedance calibration

- On-die termination (ODT)

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

7

# PCI interface

- PCI Specification Revision 2.3 compatible

- Data bus widths:

- Single 32-bit data PCI interface that operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- PCI host bridge capabilities on both interfaces

- PCI agent mode supported on PCI interface

- Support for PCI-to-memory and memory-to-PCI streaming

- Memory prefetching of PCI read accesses and support for delayed read transactions

- Support for posting of processor-to-PCI and PCI-to-memory writes

- On-chip arbitration, supporting five masters on PCI

- Support for accesses to all PCI address spaces

- Parity support

- Selectable hardware-enforced coherency

- Address translation units for address mapping between host and peripheral

- Dual address cycle supported when the device is the target

- Internal configuration registers accessible from PCI

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 133 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller

- Three protocol engines available on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Programmable interrupt controller (PIC)

- Functional and programming compatibility with the MPC8260 interrupt controller

- Support for 8 external and 35 internal discrete interrupt sources

- Support for one external (optional) and seven internal machine checkstop interrupt sources

- Programmable highest priority request

- Four groups of interrupts with programmable priority

- External and internal interrupts directed to communication processor

- Redirects interrupts to external INTA pin when in core disable mode

- Unique vector number for each interrupt source

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

### **Electrical Characteristics**

- Dual industry-standard I<sup>2</sup>C interfaces

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- System initialization data is optionally loaded from I<sup>2</sup>C-1 EPROM by boot sequencer embedded hardware

- DMA controller

- Four independent virtual channels

- Concurrent execution across multiple channels with programmable bandwidth control

- All channels accessible by local core and remote PCI masters

- Misaligned transfer capability

- Data chaining and direct mode

- Interrupt on completed segment and chain

- DMA external handshake signals: DMA\_DREQ[0:3]/DMA\_DACK[0:3]/DMA\_DONE[0:3]. There is one set for each DMA channel. The pins are multiplexed to the parallel IO pins with other QE functions.

- DUART

- Two 4-wire interfaces (RxD, TxD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- System timers

- Periodic interrupt timer

- Real-time clock

- Software watchdog timer

- Eight general-purpose timers

- IEEE Std. 1149.1<sup>TM</sup> compliant, JTAG boundary scan

- Integrated PCI bus and SDRAM clock generation

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8360E/58E. The device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

# 2.1 Overall DC Electrical Characteristics

This section covers the ratings, conditions, and other characteristics.

# 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

Table 1. Absolute Maximum Ratings<sup>1</sup>

| Characteristic                                                                                                                              |                                                                                                       |                   | Max Value                        | Unit | Notes |

|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------|----------------------------------|------|-------|

| Core supply voltage For QE frequencies <500 MHz and e300 frequencies <667 MHz For a QE frequency of 500 MHz or an e300 frequency of 667 MHz |                                                                                                       |                   | -0.3 to 1.32<br>-0.3 to 1.37     | V    |       |

| PLL supply voltage For QE frequencies <500 MHz and e300 frequencies <667 MHz For a QE frequency of 500 MHz or an e300 frequency of 667 MHz  |                                                                                                       |                   | -0.3 to 1.32<br>-0.3 to 1.37     | V    |       |

| DDR and DDR2 DR                                                                                                                             | AM I/O voltage<br>DDR<br>DDR2                                                                         | GV <sub>DD</sub>  | -0.3 to 2.75<br>-0.3 to 1.89     | V    |       |

| Three-speed Ethern                                                                                                                          | et I/O, MII management voltage                                                                        | LV <sub>DD</sub>  | -0.3 to 3.63                     | V    |       |

| PCI, local bus, DUA I <sup>2</sup> C, SPI, and JTAG                                                                                         | RT, system control and power management, I/O voltage                                                  | OV <sub>DD</sub>  | -0.3 to 3.63                     | V    |       |

| Input voltage                                                                                                                               | DDR DRAM signals                                                                                      | MV <sub>IN</sub>  | -0.3 to (GV <sub>DD</sub> + 0.3) | V    | 2, 5  |

|                                                                                                                                             | DDR DRAM reference                                                                                    | MV <sub>REF</sub> | -0.3 to (GV <sub>DD</sub> + 0.3) | V    | 2, 5  |

|                                                                                                                                             | Three-speed Ethernet signals                                                                          | LV <sub>IN</sub>  | -0.3 to (LV <sub>DD</sub> + 0.3) | V    | 4, 5  |

|                                                                                                                                             | Local bus, DUART, CLKIN, system control and power management, I <sup>2</sup> C, SPI, and JTAG signals | OV <sub>IN</sub>  | -0.3 to (OV <sub>DD</sub> + 0.3) | V    | 3, 5  |

|                                                                                                                                             | PCI                                                                                                   | OV <sub>IN</sub>  | -0.3 to (OV <sub>DD</sub> + 0.3) | V    | 6     |

| Storage temperature range                                                                                                                   |                                                                                                       | T <sub>STG</sub>  | -55 to 150                       | °C   |       |

### Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. Caution:  $MV_{IN}$  must not exceed  $GV_{DD}$  by more than 0.3 V. This limit may be exceeded for a maximum of 100 ms during power-on reset and power-down sequences.

- 3. **Caution:**  $OV_{IN}$  must not exceed  $OV_{DD}$  by more than 0.3 V. This limit may be exceeded for a maximum of 100 ms during power-on reset and power-down sequences.

- 4. **Caution:** LV<sub>IN</sub> must not exceed LV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 100 ms during power-on reset and power-down sequences.

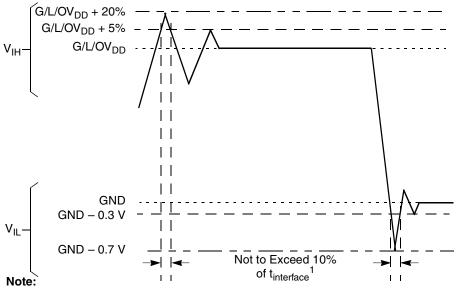

- 5.  $(M,L,O)V_{IN}$  and  $MV_{REF}$  may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 3.

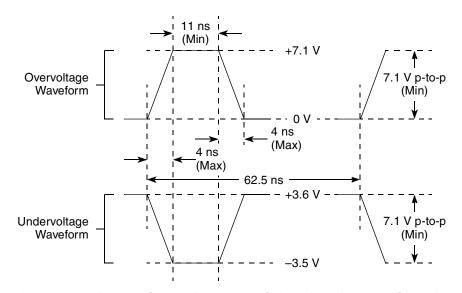

- 6. OV<sub>IN</sub> on the PCI interface may overshoot/undershoot according to the PCI Electrical Specification for 3.3-V operation, as shown in Figure 4.

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

# 2.1.2 Power Supply Voltage Specification

Table 2 provides the recommended operating conditions for the device. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

**Table 2. Recommended Operating Conditions**

| Characteristic                                                                                                                                | Symbol             | Recommended<br>Value             | Unit | Notes |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------|------|-------|

| Core supply voltage  For QE frequencies <500 MHz and e300 frequencies <667 MHz  For a QE frequency of 500 MHz or an e300 frequency of 667 MHz | V <sub>DD</sub>    | 1.2 V ± 60 mV<br>1.3 V ± 50 mV   | V    | 1     |

| PLL supply voltage For QE frequencies <500 MHz and e300 frequencies <667 MHz For a QE frequency of 500 MHz or an e300 frequency of 667 MHz    | AV <sub>DD</sub>   | 1.2 V ± 60 mV<br>1.3 V ± 50 mV   | V    | 1     |

| DDR and DDR2 DRAM I/O supply voltage  DDR  DDR2                                                                                               | GV <sub>DD</sub>   | 2.5 V ± 125 mV<br>1.8V ± 90 mV   | V    |       |

| Three-speed Ethernet I/O supply voltage                                                                                                       | LV <sub>DD</sub> 0 | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    |       |

| Three-speed Ethernet I/O supply voltage                                                                                                       | LV <sub>DD</sub> 1 | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    |       |

| Three-speed Ethernet I/O supply voltage                                                                                                       | LV <sub>DD</sub> 2 | 3.3 V ± 330 mV<br>2.5 V ± 125 mV | V    |       |

| PCI, local bus, DUART, system control and power management, I <sup>2</sup> C, SPI, and JTAG I/O voltage                                       | OV <sub>DD</sub>   | 3.3 V ± 330 mV                   | V    |       |

| Junction temperature                                                                                                                          | T <sub>J</sub>     | 0 to 105                         | °C   | 2     |

### Notes:

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

<sup>2. .</sup>The operating conditions for junction temperature,  $T_J$ , on the 600/333/400 MHz and 500/333/500 MHz on rev2.0 silicon is 0 °C to 70 °C. Please refer to *General9* in the device errata document.

1. Note that  $t_{\text{interface}}$  refers to the clock period associated with the bus clock interface.

Figure 3. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>

Figure 4 shows the undershoot and overshoot voltage of the PCI interface of the device for the 3.3-V signals, respectively.

Figure 4. Maximum AC Waveforms on PCI interface for 3.3-V Signaling

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

# 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

**Table 3. Output Drive Capability**

| Driver Type                                        | Output Impedance (Ω)                       | Supply Voltage                                             |

|----------------------------------------------------|--------------------------------------------|------------------------------------------------------------|

| Local bus interface utilities signals              | 42                                         | OV <sub>DD</sub> = 3.3 V                                   |

| PCI signals                                        | 25                                         |                                                            |

| PCI output clocks (including PCI_SYNC_OUT)         | 42                                         |                                                            |

| DDR signal                                         | 20<br>36 (half strength mode) <sup>1</sup> | GV <sub>DD</sub> = 2.5 V                                   |

| DDR2 signal                                        | 18<br>36 (half strength mode) <sup>1</sup> | GV <sub>DD</sub> = 1.8 V                                   |

| 10/100/1000 Ethernet signals                       | 42                                         | LV <sub>DD</sub> = 2.5/3.3 V                               |

| DUART, system control, I <sup>2</sup> C, SPI, JTAG | 42                                         | OV <sub>DD</sub> = 3.3 V                                   |

| GPIO signals                                       | 42                                         | $OV_{DD} = 3.3 \text{ V}$<br>$LV_{DD} = 2.5/3.3 \text{ V}$ |

<sup>1</sup> DDR output impedance values for half strength mode are verified by design and not tested

# 2.2 Power Sequencing

This section details the power sequencing considerations for the MPC8360E/58E.

# 2.2.1 Power-Up Sequencing

MPC8360E/58E does not require the core supply voltage ( $V_{DD}$  and  $AV_{DD}$ ) and I/O supply voltages ( $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ ) to be applied in any particular order. During the power ramp up, before the power supplies are stable and if the I/O voltages are supplied before the core voltage, there may be a period of time that all input and output pins will actively be driven and cause contention and excessive current. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the core voltage ( $V_{DD}$ ) before the I/O voltage ( $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ ) and assert  $\overline{PORESET}$  before the power

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V, see Figure 5.

Voltage A I/O Voltage (GV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>)

Core Voltage (V<sub>DD</sub>, AV<sub>DD</sub>)

0.7 V

Figure 5. Power Sequencing Example

I/O voltage supplies ( $GV_{DD}$ ,  $LV_{DD}$ , and  $OV_{DD}$ ) do not have any ordering requirements with respect to one another.

# 2.2.2 Power-Down Sequencing

The MPC8360E/58E does not require the core supply voltage and I/O supply voltages to be powered-down in any particular order.

# 3 Power Characteristics

The estimated typical power dissipation values are shown in Table 4 and Table 5.

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Typical | Maximum | Unit | Notes      |

|-------------------------|------------------------|---------------------------------|---------|---------|------|------------|

| 266                     | 266                    | 500                             | 5.0     | 5.6     | W    | 2, 3, 5    |

| 400                     | 266                    | 400                             | 4.5     | 5.0     | W    | 2, 3, 4    |

| 533                     | 266                    | 400                             | 4.8     | 5.3     | W    | 2, 3, 4    |

| 667                     | 333                    | 400                             | 5.8     | 6.3     | W    | 3, 6, 7, 8 |

| 500                     | 333                    | 500                             | 5.9     | 6.4     | W    | 3, 6, 7, 8 |

Table 4. MPC8360E TBGA Core Power Dissipation<sup>1</sup>

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

### **Power Characteristics**

# Table 4. MPC8360E TBGA Core Power Dissipation<sup>1</sup> (continued)

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Typical | Maximum | Unit | Notes      |

|-------------------------|------------------------|---------------------------------|---------|---------|------|------------|

| 667                     | 333                    | 500                             | 6.1     | 6.8     | W    | 2, 3, 5, 9 |

### Notes:

- 1. The values do not include I/O supply power (OV<sub>DD</sub>, LV<sub>DD</sub>, GV<sub>DD</sub>) or AV<sub>DD</sub>. For I/O power values, see Table 6.

- 2. Typical power is based on a voltage of V<sub>DD</sub> = 1.2 V or 1.3 V, a junction temperature of T<sub>J</sub> = 105°C, and a Dhrystone benchmark application.

- Thermal solutions will likely need to design to a value higher than typical power on the end application, T<sub>A</sub> target, and I/O power.

- 4. Maximum power is based on a voltage of  $V_{DD} = 1.2 \text{ V}$ , WC process, a junction  $T_J = 105^{\circ}\text{C}$ , and an artificial smoke test.

- 5. Maximum power is based on a voltage of  $V_{DD} = 1.3 \text{ V}$  for applications that use 667MHz(CPU)/500(QE) with WC process, a junction  $T_J = 105$ °C, and an artificial smoke test.

- 6. Typical power is based on a voltage of V<sub>DD</sub> = 1.3 V, a junction temperature of T<sub>J</sub> = 70°C, and a Dhrystone benchmark application.

- 7. Maximum power is based on a voltage of  $V_{DD} = 1.3 \text{ V}$  for applications that use 667MHz(CPU) or 500(QE) with WC process, a junction  $T_J = 70^{\circ}\text{C}$ , and an artificial smoke test.

- 8. This frequency combination is only available for rev2.0 silicon.

- 9. This frequency combination is not available for rev2.0 silicon.

# Table 5. MPC8358E TBGA Core Power Dissipation<sup>1</sup>

| Core<br>Frequency (MHz) | CSB<br>Frequency (MHz) | QUICC Engine<br>Frequency (MHz) | Typical | Maximum | Unit | Notes   |

|-------------------------|------------------------|---------------------------------|---------|---------|------|---------|

| 266                     | 266                    | 300                             | 4.1     | 4.5     | W    | 2, 3, 4 |

| 400                     | 266                    | 400                             | 4.5     | 5.0     | W    | 2, 3, 4 |

### Notes:

- 1. The values do not include I/O supply power (OV $_{DD}$ , LV $_{DD}$ , GV $_{DD}$ ) or AV $_{DD}$ . For I/O power values, see Table 6.

- Typical power is based on a voltage of V<sub>DD</sub> = 1.2 V, a junction temperature of T<sub>J</sub> = 105°C, and a Dhrystone benchmark application.

- Thermal solutions will likely need to design to a value higher than typical power on the end application, T<sub>A</sub> target, and I/O power.

- 4. Maximum power is based on a voltage of  $V_{DD} = 1.2 \text{ V}$ , WC process, a junction  $T_J = 105^{\circ}\text{C}$ , and an artificial smoke test.

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

Table 6 shows the estimated typical I/O power dissipation for the device.

Table 6. Estimated Typical I/O Power Dissipation

| Interface                    | Parameter          | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | OV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(2.5 V) | Unit | Comments            |

|------------------------------|--------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------|---------------------|

| DDR I/O                      | 200 MHz, 1x32 bits | 0.3                         | 0.46                        |                             |                             |                             | W    |                     |

| $R_s = 20 Ω$                 | 200 MHz, 1x64 bits | 0.4                         | 0.58                        |                             |                             |                             | W    |                     |

| $R_t = 50 \Omega$            | 200 MHz, 2x32 bits | 0.6                         | 0.92                        |                             |                             |                             | W    |                     |

| 2 pairs of clocks            | 266 MHz, 1x32 bits | 0.35                        | 0.56                        |                             |                             |                             | W    |                     |

| CIOCKS                       | 266 MHz, 1x64 bits | 0.46                        | 0.7                         |                             |                             |                             | W    |                     |

|                              | 266 MHz, 2x32 bits | 0.7                         | 1.11                        |                             |                             |                             | W    |                     |

|                              | 333 MHz, 1x32 bits | 0.4                         | 0.65                        |                             |                             |                             | W    |                     |

|                              | 333 MHz, 1x64 bits | 0.53                        | 0.82                        |                             |                             |                             | W    |                     |

|                              | 333 MHz, 2x32 bits | 0.81                        | 1.3                         |                             |                             |                             | W    |                     |

| Local Bus I/O                | 133 MHz, 32 bits   |                             |                             | 0.22                        |                             |                             | W    |                     |

| Load = 25 pf<br>3 pairs of   | 83 MHz, 32 bits    |                             |                             | 0.14                        |                             |                             | W    |                     |

| clocks                       | 66 MHz, 32 bits    |                             |                             | 0.12                        |                             |                             | W    |                     |

|                              | 50 MHz, 32 bits    |                             |                             | 0.09                        |                             |                             | W    |                     |

| PCI I/O                      | 33 MHz, 32 bits    |                             |                             | 0.05                        |                             |                             | W    |                     |

| Load = 30 pf                 | 66 MHz, 32 bits    |                             |                             | 0.07                        |                             |                             | W    |                     |

| 10/100/1000                  | MII or RMII        |                             |                             |                             | 0.01                        |                             | W    | Multiply by number  |

| Ethernet I/O<br>Load = 20 pf | GMII or TBI        |                             |                             |                             | 0.04                        |                             | W    | of interfaces used. |

|                              | RGMII or RTBI      |                             |                             |                             |                             | 0.04                        | W    |                     |

| Other I/O                    |                    |                             |                             | 0.1                         |                             |                             | W    |                     |

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8360E/58E.

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

# 4.1 DC Electrical Characteristics

Table 7 provides the clock input (CLKIN/PCI\_SYNC\_IN) DC timing specifications for the device.

Table 7. CLKIN DC Electrical Characteristics

| Parameter                 | Condition                                                                                       | Symbol          | Min  | Max                    | Unit |

|---------------------------|-------------------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| Input high voltage        | _                                                                                               | V <sub>IH</sub> | 2.7  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage         | _                                                                                               | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| CLKIN input current       | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{OV}_{\text{DD}}$                              | I <sub>IN</sub> | _    | ±10                    | μΑ   |

| PCI_SYNC_IN input current | $0 \text{ V} \le V_{IN} \le 0.5 \text{V or}$<br>$OV_{DD} - 0.5 \text{V} \le V_{IN} \le OV_{DD}$ | I <sub>IN</sub> | _    | ±10                    | μΑ   |

| PCI_SYNC_IN input current | $0.5 \text{ V} \le V_{IN} \le OV_{DD} - 0.5 \text{ V}$                                          | I <sub>IN</sub> | _    | ±100                   | μΑ   |

# 4.2 AC Electrical Characteristics

The primary clock source for the device can be one of two inputs, CLKIN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. Table 8 provides the clock input (CLKIN/PCI\_CLK) AC timing specifications for the device.

**Table 8. CLKIN AC Timing Specifications**

| Parameter/Condition              | Symbol                               | Min | Typical | Max   | Unit | Notes |

|----------------------------------|--------------------------------------|-----|---------|-------|------|-------|

| CLKIN/PCI_CLK frequency          | f <sub>CLKIN</sub>                   | _   | _       | 66.67 | MHz  | 1     |

| CLKIN/PCI_CLK cycle time         | t <sub>CLKIN</sub>                   | 15  | _       | _     | ns   | _     |

| CLKIN/PCI_CLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>    | 0.6 | 1.0     | 2.3   | ns   | 2     |

| CLKIN/PCI_CLK duty cycle         | t <sub>KHK</sub> /t <sub>CLKIN</sub> | 40  | _       | 60    | %    | 3     |

| CLKIN/PCI_CLK jitter             | _                                    | _   | _       | ±150  | ps   | 4, 5  |

### Notes:

- 1. **Caution:** The system, core, USB, security, and 10/100/1000 Ethernet must not exceed their respective maximum or minimum operating frequencies.

- 2. Rise and fall times for CLKIN/PCI\_CLK are measured at 0.4 V and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The CLKIN/PCI\_CLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track CLKIN drivers with the specified jitter.

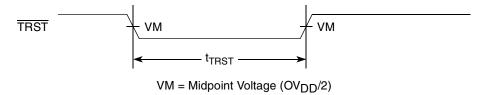

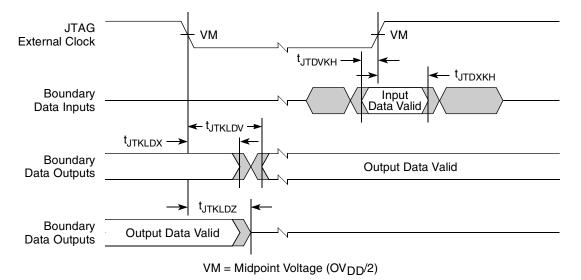

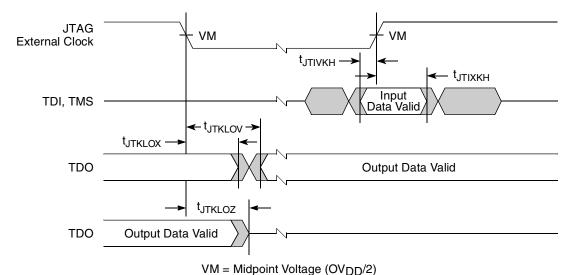

# 5 RESET Initialization

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the MPC8360E/58E.

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

# 5.1 RESET DC Electrical Characteristics

Table 9 provides the DC electrical characteristics for the RESET pins of the device.

**Table 9. RESET Pins DC Electrical Characteristics**

| Characteristic      | Symbol          | Condition                  | Min  | Max                    | Unit |

|---------------------|-----------------|----------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> |                            | 2.0  | OV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> |                            | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> |                            |      | ±10                    | μΑ   |

| Output high voltage | V <sub>OH</sub> | $I_{OH} = -8.0 \text{ mA}$ | 2.4  | _                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA   | _    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA   |      | 0.4                    | V    |

### Notes:

- 1. This table applies for pins PORESET, HRESET, SRESET and QUIESCE.

- 2.  $\overline{\text{HRESET}}$  and  $\overline{\text{SRESET}}$  are open drain pins, thus  $V_{OH}$  is not relevant for those pins.

# 5.2 RESET AC Electrical Characteristics

This section describes the AC electrical specifications for the reset initialization timing requirements of the device. Table 10 provides the reset initialization AC timing specifications for the DDR SDRAM component(s).

**Table 10. RESET Initialization Timing Specifications**

| Parameter/Condition                                                                                                                                        | Min | Max | Unit                     | Notes |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|-------|

| Required assertion time of HRESET or SRESET (input) to activate reset flow                                                                                 | 32  | _   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Required assertion time of PORESET with stable clock applied to CLKIN when the device is in PCI host mode                                                  | 32  | _   | <sup>t</sup> CLKIN       | 2     |

| Required assertion time of PORESET with stable clock applied to PCI_SYNC_IN when the device is in PCI agent mode                                           | 32  | _   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET/SRESET assertion (output)                                                                                                                           | 512 | _   | t <sub>PCI_SYNC_IN</sub> | 1     |

| HRESET negation to SRESET negation (output)                                                                                                                | 16  | _   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI host mode  | 4   | _   | <sup>†</sup> CLKIN       | 2     |

| Input setup time for POR config signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI agent mode | 4   | _   | t <sub>PCI_SYNC_IN</sub> | 1     |

| Input hold time for POR config signals with respect to negation of HRESET                                                                                  | 0   | _   | ns                       |       |

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

**Table 10. RESET Initialization Timing Specifications (continued)**

| Time for the device to turn off POR config signals with respect to the assertion of HRESET | _ | 4 | ns                       | 3    |

|--------------------------------------------------------------------------------------------|---|---|--------------------------|------|

| Time for the device to turn on POR config signals with respect to the negation of HRESET   | 1 | 1 | t <sub>PCI_SYNC_IN</sub> | 1, 3 |

### Notes:

- 1. t<sub>PCI\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. When the device is In PCI host mode the primary clock is applied to the CLKIN input, and PCI\_SYNC\_IN period depends on the value of CFG\_CLKIN\_DIV. See the MPC8360E Integrated Communications Processor Reference Manual, Rev. 2 for more details.

- 2. t<sub>CLKIN</sub> is the clock period of the input clock applied to CLKIN. It is only valid when the device is in PCI host mode. See the *MPC8360E Integrated Communications Processor Reference Manual, Rev. 2* for more details.

- 3. POR config signals consists of CFG\_RESET\_SOURCE[0:2] and CFG\_CLKIN\_DIV.

Table 11 provides the PLL and DLL lock times.

Table 11. PLL and DLL Lock Times

| Parameter/Condition | Min  | Max     | Unit           | Notes |

|---------------------|------|---------|----------------|-------|

| PLL lock times      | _    | 100     | μs             |       |

| DLL lock times      | 7680 | 122,880 | csb_clk cycles | 1, 2  |

### Notes:

- DLL lock times are a function of the ratio between the output clock and the coherency system bus clock (csb\_clk).

A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

- 2. The csb\_clk is determined by the CLKIN and system PLL ratio. See Section 22, "Clocking," for more information.

# 5.3 QE Operating Frequency Limitations

This section specify the limits of the AC electrical characteristics for the operation of the QE's communication interfaces.

### NOTE

The settings listed below are required for correct hardware interface operation. Each protocol by itself requires a minimal QE operating frequency setting for meeting the performance target. Because the performance is a complex function of all the QE settings, the user should make use of the QE performance utility tool provided by Freescale to validate their system.

Table 12 lists the maximal QE I/O frequencies and the minimal QE core frequency for each interface.

**Table 12. QE Operating Frequency Limitations**

| Interface                        | Interface Operating Frequency (MHz) | Max interface<br>Bit Rate (Mbps) | Min QE Operating Frequency <sup>1</sup> (MHz) | Notes |

|----------------------------------|-------------------------------------|----------------------------------|-----------------------------------------------|-------|

| Ethernet Management:<br>MDC/MDIO | 10 (max)                            | 10                               | 20                                            |       |

| MII                              | 25 (typ)                            | 100                              | 50                                            |       |

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

**Table 12. QE Operating Frequency Limitations (continued)**

| (typ)<br>5 (typ)<br>(max) | 100                                                                 | 50<br>250                                                                                                                                                |                                                                                                                                                                                                                          |

|---------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |                                                                     | 250                                                                                                                                                      |                                                                                                                                                                                                                          |

| (max)                     | 40                                                                  |                                                                                                                                                          |                                                                                                                                                                                                                          |

|                           | 10                                                                  | 20                                                                                                                                                       |                                                                                                                                                                                                                          |

| (max)                     | 70                                                                  | 8×F                                                                                                                                                      | 2                                                                                                                                                                                                                        |

| (max)                     | 16.67                                                               | 16 × F                                                                                                                                                   | 2, 4                                                                                                                                                                                                                     |

| (max)                     | 800                                                                 | 2×F                                                                                                                                                      | 2                                                                                                                                                                                                                        |

| (max)                     | 800                                                                 | 2×F                                                                                                                                                      | 2                                                                                                                                                                                                                        |

| (max)                     | 10                                                                  | 20                                                                                                                                                       |                                                                                                                                                                                                                          |

| (max)                     | 50                                                                  | 8/3 × F                                                                                                                                                  | 2, 3                                                                                                                                                                                                                     |

| x internal ref<br>lock)   | 115 (Kbps)                                                          | 20                                                                                                                                                       |                                                                                                                                                                                                                          |

| (max)                     | 2                                                                   | 20                                                                                                                                                       |                                                                                                                                                                                                                          |

| ef clock)                 | 12                                                                  | 96                                                                                                                                                       |                                                                                                                                                                                                                          |

|                           | (max) (max) (max) (max) (max) (max) (max) x internal reflock) (max) | (max)     16.67       (max)     800       (max)     800       (max)     10       (max)     50       x internal reflock)     115 (Kbps)       (max)     2 | (max)     16.67     16 × F       (max)     800     2 × F       (max)     800     2 × F       (max)     10     20       (max)     50     8/3 × F       x internal reflock)     115 (Kbps)     20       (max)     2     20 |

### Note:

- 1. The QE needs to run at a frequency higher than or equal to what is listed in this table.

- 2. 'F' is the actual interface operating frequency.

- 3. The bit rate limit is independent of the data bus width (i.e. the same for serial, nibble, or octal interfaces).

- 4. TDM in high-speed mode for serial data interface.

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR and DDR2 SDRAM interface of the MPC8360E/58E.

# 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

Table 13 provides the recommended operating conditions for the DDR2 SDRAM component(s) of the device when  $GV_{DD}(typ) = 1.8 \text{ V}$ .

Table 13. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

| Parameter/Condition     | Symbol            | Min                                 | Max                                 | Unit | Notes |

|-------------------------|-------------------|-------------------------------------|-------------------------------------|------|-------|

| I/O supply voltage      | GV <sub>DD</sub>  | 1.71                                | 1.89                                | V    | 1     |

| I/O reference voltage   | MV <sub>REF</sub> | $0.49 \times \text{GV}_{\text{DD}}$ | $0.51 \times \text{GV}_{\text{DD}}$ | V    | 2     |

| I/O termination voltage | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04            | MV <sub>REF</sub> + 0.04            | V    | 3     |

| Input high voltage      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125           | GV <sub>DD</sub> + 0.3              | V    |       |

| Input low voltage       | V <sub>IL</sub>   | -0.3                                | MV <sub>REF</sub> – 0.125           | V    |       |

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

### **DDR and DDR2 SDRAM**

Table 13. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V (continued)

| Output leakage current                                              | l <sub>OZ</sub>   | _     | ±10 | μΑ | 4 |

|---------------------------------------------------------------------|-------------------|-------|-----|----|---|

| Output high current (V <sub>OUT</sub> = 1.420 V)                    | Іон               | -13.4 | _   | mA |   |

| Output low current (V <sub>OUT</sub> = 0.280 V)                     | I <sub>OL</sub>   | 13.4  | _   | mA |   |

| MV <sub>REF</sub> input leakage current                             | I <sub>VREF</sub> | _     | ±10 | μΑ |   |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ OV <sub>DD</sub> ) | I <sub>IN</sub>   | _     | ±10 | μА |   |

### Notes:

- 1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

- 2.  $MV_{REF}$  is expected to equal  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  cannot exceed  $\pm 2\%$  of the DC value.

- V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to equal MV<sub>REF</sub> This rail should track variations in the DC level of MV<sub>REF</sub>

- 4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

Table 14 provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8 \text{ V}$ .

Table 14. DDR2 SDRAM Capacitance for GV<sub>DD</sub>(typ)=1.8 V

| Parameter/Condition                          | Symbol           | Min | Max | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1     |

### Note:

1. This parameter is sampled.  $GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz,  $T_A = 25^{\circ}\text{C}$ ,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

Table 15 provides the recommended operating conditions for the DDR SDRAM component(s) of the device when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

Table 15. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                             | Symbol            | Min                                 | Max                                 | Unit | Notes |

|-------------------------------------------------|-------------------|-------------------------------------|-------------------------------------|------|-------|

| I/O supply voltage                              | GV <sub>DD</sub>  | 2.375                               | 2.625                               | V    | 1     |

| I/O reference voltage                           | MV <sub>REF</sub> | $0.49 \times \text{GV}_{\text{DD}}$ | $0.51 \times \text{GV}_{\text{DD}}$ | V    | 2     |

| I/O termination voltage                         | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04            | MV <sub>REF</sub> + 0.04            | V    | 3     |

| Input high voltage                              | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.18            | GV <sub>DD</sub> + 0.3              | V    |       |

| Input low voltage                               | V <sub>IL</sub>   | -0.3                                | MV <sub>REF</sub> – 0.18            | V    |       |

| Output leakage current                          | l <sub>OZ</sub>   | _                                   | ±10                                 | μΑ   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub>   | -15.2                               | _                                   | mA   |       |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | l <sub>OL</sub>   | 15.2                                | _                                   | mA   |       |

| MV <sub>REF</sub> input leakage current         | I <sub>VREF</sub> | _                                   | ±10                                 | μΑ   |       |

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

Table 15. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V (continued)

| Input current (0 V ≤V <sub>IN</sub> ≤ OV <sub>DD</sub> ) | I <sub>IN</sub> | _ | ±10 | μА |  |

|----------------------------------------------------------|-----------------|---|-----|----|--|

|----------------------------------------------------------|-----------------|---|-----|----|--|

### Notes:

- 1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

- 2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

- 3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

- 4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

Table 16 provides the DDR capacitance when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

Table 16. DDR SDRAM Capacitance for  $GV_{DD}(typ) = 2.5 \text{ V}$

| Parameter/Condition                     | Symbol           | Min | Max | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1     |

### Note:

# 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR and DDR2 SDRAM interface.

# 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

Table 17 provides the input AC timing specifications for the DDR2 SDRAM interface when  $GV_{DD}(typ) = 1.8 \text{ V}$ .

Table 17. DDR2 SDRAM Input AC Timing Specifications for  $GV_{DD}(typ) = 1.8 \text{ V}$

At recommended operating conditions with  $GV_{DD}$  of 1.8 V ± 5%.

| Parameter             | Symbol          | Min                      | Max                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> - 0.25 | V    |       |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | _                        | V    |       |

Table 18 provides the input AC timing specifications for the DDR SDRAM interface when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

Table 18. DDR SDRAM Input AC Timing Specifications Mode for GV<sub>DD</sub>(typ) = 2.5 V

At recommended operating conditions with GV  $_{DD}$  of 2.5 V  $\pm$  5%.

| Parameter            | Symbol   | Min | Max                      | Unit | Notes |

|----------------------|----------|-----|--------------------------|------|-------|

| AC input low voltage | $V_{IL}$ | _   | MV <sub>REF</sub> – 0.31 | V    |       |

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

<sup>1.</sup> This parameter is sampled.  $GV_{DD} = 2.5 \text{ V} \pm 0.125 \text{ V}$ , f = 1 MHz,  $T_A = 25^{\circ}\text{C}$ ,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak to peak) = 0.2 V.

### **DDR and DDR2 SDRAM**

# Table 18. DDR SDRAM Input AC Timing Specifications Mode for GV<sub>DD</sub>(typ) = 2.5 V (continued)

At recommended operating conditions with GV  $_{DD}$  of 2.5 V  $\pm$  5%.

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | _ | V |  |  |

|-----------------------|-----------------|--------------------------|---|---|--|--|

|-----------------------|-----------------|--------------------------|---|---|--|--|

### Notes:

1. Maximum possible skew between a data strobe (MDQS[n]) and any corresponding bit of data (MDQ[8n +  $\{0...7\}$ ] if  $0 \le n \le 7$ ) or ECC (MECC[ $\{0...7\}$ ] if n = 8).

Table 19. DDR and DDR2 SDRAM Input AC Timing Specifications Mode for  $GV_{DD}(typ) = 2.5 \text{ V}$  At recommended operating conditions with  $GV_{DD}$  of 2.5 V  $\pm$  5%.

| Parameter                                                          | Symbol | Min                    | Max                 | Unit | Notes |

|--------------------------------------------------------------------|--------|------------------------|---------------------|------|-------|

| MDQS—MDQ/MECC input skew per byte<br>333 MHz<br>266 MHz<br>200 MHz |        | -750<br>-1125<br>-1250 | 750<br>1125<br>1250 | ps   | 1, 2  |

### Notes:

- 1. AC timing values are based on the DDR data rate, which is twice the DDR memory bus frequency.

- 2. Maximum possible skew between a data strobe (MDQS[n]) and any corresponding bit of data (MDQ[8n +  $\{0...7\}$ ] if  $0 \le n \le 7$ ) or ECC (MECC[ $\{0...7\}$ ] if n = 8).

# 6.2.2 DDR and DDR2 SDRAM Output AC Timing Specifications

Table 20 and Table 21 provide the output AC timing specifications and measurement conditions for the DDR and DDR2 SDRAM interface.

Table 20. DDR and DDR2 SDRAM Output AC Timing Specifications for Source Synchronous Mode At recommended operating conditions with  $GV_{DD}$  of (1.8 V or 2.5 V)  $\pm$  5%.

| Parameter <sup>8</sup>                                                                 | Symbol <sup>1</sup> | Min                  | Max               | Unit | Notes |

|----------------------------------------------------------------------------------------|---------------------|----------------------|-------------------|------|-------|

| MCK[n] cycle time, (MCK[n]/MCK[n] crossing)                                            | t <sub>MCK</sub>    | 6                    | 10                | ns   | 2     |

| Skew between any MCK to ADDR/CMD  333 MHz 266 MHz 200 MHz                              |                     | -1.0<br>-1.1<br>-1.2 | 0.2<br>0.3<br>0.4 | ns   | 3     |

| ADDR/CMD output setup with respect to MCK 333 MHz 266 MHz 200 MHz                      |                     | 2.1<br>2.8<br>3.5    | _                 | ns   | 4     |

| ADDR/CMD output hold with respect to MCK 333 MHz 266 MHz - DDR1 266 MHz - DDR2 200 MHz |                     | 2.0<br>2.72.8<br>3.5 | _                 | ns   | 4     |

| MCS(n) output setup with respect to MCK  333 MHz 266 MHz 200 MHz                       |                     | 2.1<br>2.8<br>3.5    | _                 | ns   | 4     |

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

Table 20. DDR and DDR2 SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

| Parameter <sup>8</sup>                                                          | Symbol <sup>1</sup>                                     | Min                         | Max                         | Unit | Notes |

|---------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------|-----------------------------|------|-------|

| MCS(n) output hold with respect to MCK  333 MHz 266 MHz 200 MHz                 | t <sub>DDKHCX</sub>                                     | 2.0<br>2.7<br>3.5           | _                           | ns   | 4     |

| MCK to MDQS                                                                     | t <sub>DDKHMH</sub>                                     | -0.8                        | 0.7                         | ns   | 5, 9  |

| MDQ/MECC/MDM output setup with respect to MDQS<br>333 MHz<br>266 MHz<br>200 MHz | <sup>t</sup> DDKHDS <sup>,</sup><br><sup>t</sup> DDKLDS | 0.7<br>1.0<br>1.2           | _                           | ns   | 6     |

| MDQ/MECC/MDM output hold with respect to MDQS<br>333 MHz<br>266 MHz<br>200 MHz  | <sup>†</sup> DDKHDX <sup>,</sup><br><sup>†</sup> DDKLDX | 0.7<br>1.0<br>1.2           | _                           | ns   | 6     |

| MDQS preamble start                                                             | t <sub>DDKHMP</sub>                                     | $-0.5 \times t_{MCK} - 0.6$ | $-0.5 \times t_{MCK} + 0.6$ | ns   | 7     |

| MDQS epilogue end                                                               | t <sub>DDKHME</sub>                                     | -0.6                        | 0.9                         | ns   | 7     |

### Notes:

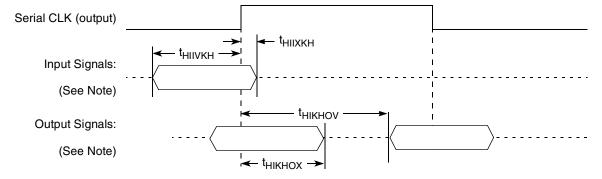

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)</sub>(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

- 2. All MCK/ $\overline{\text{MCK}}$  referenced measurements are made from the crossing of the two signals  $\pm 0.1$  V.

- 3. In the source synchronous mode, MCK/MCK can be shifted in 1/4 applied cycle increments through the Clock Control Register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- 4. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the Clock Control register is set to adjust the memory clocks by 1/2 applied cycle.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this will typically be set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8360E Integrated Communications Processor Reference Manual, Rev. 2 for a description and understanding of the timing modifications enabled by use of these bits.

- 6. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the device.

- 7. All outputs are referenced to the rising edge of MCK(n) at the pins of the device. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

- 8. AC timing values are based on the DDR data rate, which is twice the DDR memory bus frequency.

- 9. In rev2.0 silicon, t<sub>DDKHMH</sub> maximum meets the specification of 0.6ns. In rev 2.0 silicon, due to errata, t<sub>DDKHMH</sub> minimum is -0.9 ns. Please refer to *DDR18* in the device errata document.

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

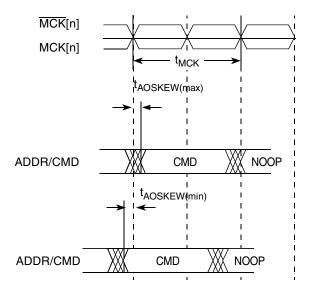

Figure 6 shows the DDR SDRAM output timing for address skew with respect to any MCK.

Figure 6. Timing Diagram for  $t_{\text{AOSKEW}}$  Measurement

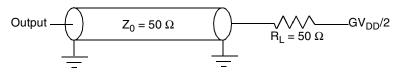

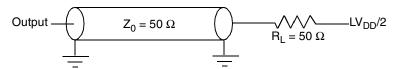

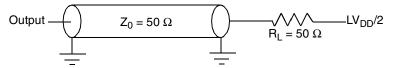

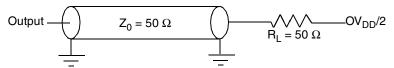

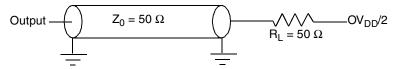

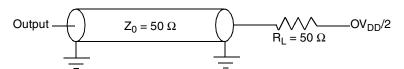

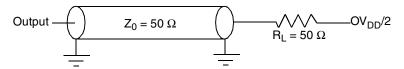

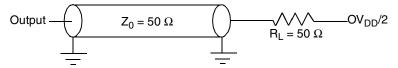

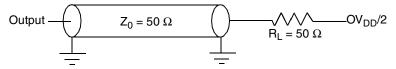

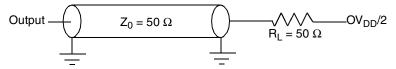

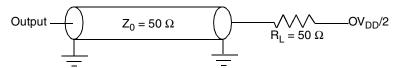

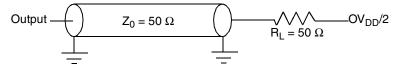

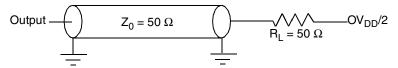

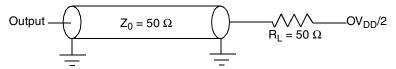

Figure 7 provides the AC test load for the DDR bus.

Figure 7. DDR AC Test Load

Table 21. DDR and DDR2 SDRAM Measurement Conditions

| Symbol           | DDR                                | DDR2                               | Unit | Notes |

|------------------|------------------------------------|------------------------------------|------|-------|

| V <sub>TH</sub>  | MV <sub>REF</sub> ± 0.31 V         | MV <sub>REF</sub> ± 0.25 V         | V    | 1     |

| V <sub>OUT</sub> | $0.5 \times \text{GV}_{\text{DD}}$ | $0.5 \times \text{GV}_{\text{DD}}$ | V    | 2     |

### Notes:

- 1. Data input threshold measurement point.

- 2. Data output measurement point.

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

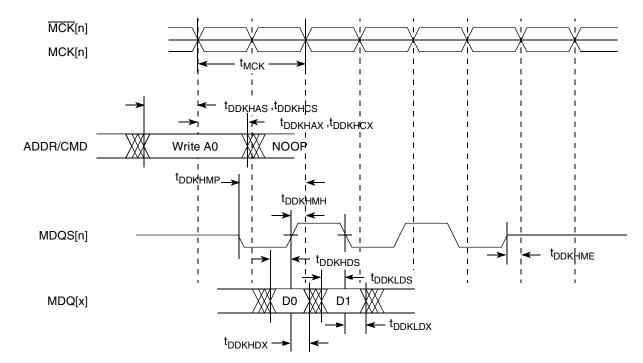

Figure 8 shows the DDR SDRAM output timing diagram for source synchronous mode.

Figure 8. DDR SDRAM Output Timing Diagram for Source Synchronous Mode

Table 22 provides approximate delay information that can be expected for the address and command signals of the DDR controller for various loadings, which can be useful for a system utilizing the DLL. These numbers are the result of simulations for one topology. The delay numbers will strongly depend on the topology used. These delay numbers show the total delay for the address and command to arrive at the DRAM devices. The actual delay could be different than the delays seen in simulation, depending on the system topology. If a heavily loaded system is used, the DLL loop may need to be adjusted to meet setup requirements at the DRAM.

| Load                                               | Delay | Unit |

|----------------------------------------------------|-------|------|

| 4 devices (12 pF)                                  | 3.0   | ns   |

| 9 devices (27 pF)                                  | 3.6   | ns   |

| 36 devices (108 pF) + 40 pF compensation capacitor | 5.0   | ns   |

| 36 devices (108 pF) + 80 pF compensation capacitor | 5.2   | ns   |

Table 22. Expected Delays for Address/Command

MPC8360E/MPC8358E PowerQUICC™ II Pro Processor Revision 2.x TBGA Silicon Hardware Specifications, Rev. 2

**DUART**

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the MPC8360E/58E.

# 7.1 DUART DC Electrical Characteristics

Table 23 provides the DC electrical characteristics for the DUART interface of the device.

Table 23. DUART DC Electrical Characteristics

| Parameter                                          | Symbol          | Min                    | Max                    | Unit | Notes |

|----------------------------------------------------|-----------------|------------------------|------------------------|------|-------|

| High-level input voltage                           | V <sub>IH</sub> | 2                      | OV <sub>DD</sub> + 0.3 | V    |       |

| Low-level input voltage OV <sub>DD</sub>           | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |       |

| High-level output voltage, $I_{OH} = -100 \mu A$   | V <sub>OH</sub> | OV <sub>DD</sub> – 0.4 | _                      | V    |       |

| Low-level output voltage, I <sub>OL</sub> = 100 μA | V <sub>OL</sub> | _                      | 0.2                    | V    |       |

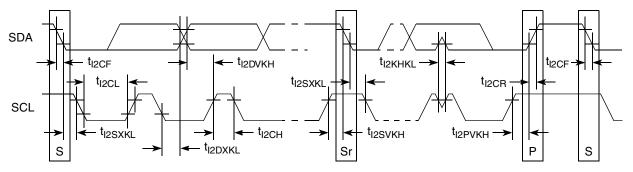

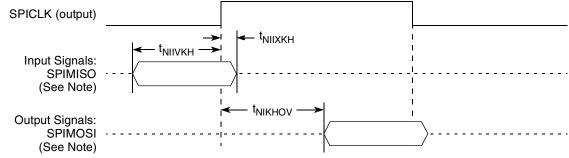

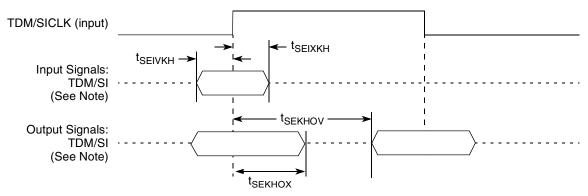

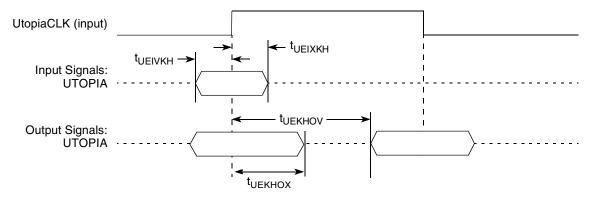

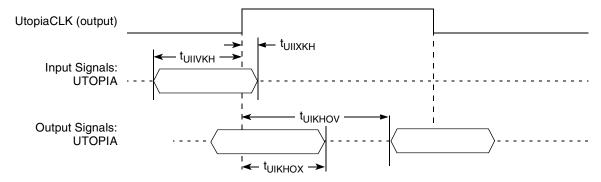

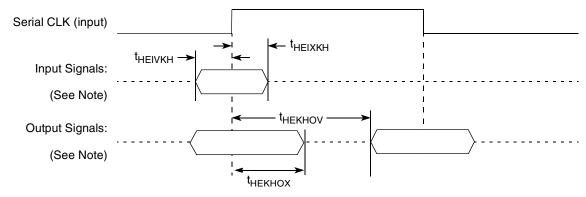

| Input current (0 $V \le V_{IN} \le OV_{DD}$ )      | I <sub>IN</sub> | _                      | ±10                    | μΑ   | 1     |